PCIe(PCI Express) Pin Map 분석 (ft.그래픽카드)

D.U.T 2022. 5. 29. 09:23

<자료원문: https://designusefulthings.tistory.com/33 >

■ PCIe(PCI Express)란 무엇인가?

PCIe(PCI Express)는 일반적으로 고속 직렬 컴퓨터 확장 버스 표준을 말합니다.

쉽게 설명드리면 장치들 사이에 아주 빠른 통신을 주고 받기 위해 태어났습니다. 기술이 발달하기 전에는 병렬 통신 방법이 직렬 통신 방법보다 속도가 빨랐습니다. 하지만 기술 발전이 이루어지면서 병렬 통신에 문제점들(신호 동기화, 지연(Latency), 많은 데이터 라인)이 나타났습니다. 병렬 통신의 문제점들은 통신을 아주 빠르게 하는데 문제가 있어서 직렬 통신을 고속화하여 현재는 사용하고 있습니다.

PCI 익스프레스(PCI Express)는 입출력 직렬 구조 인터페이스

PCIe(PCI Express)는 고대역폭, 작은 핀 수, 직렬 통신 연결 기술입니다. 그러므로 PCIe(PCI Express)는 아래와 같은 특징을 가지고 있습니다.

1. 높은 최대 시스템 버스 처리량

2. 작은 I/O 핀 수 및 작은 물리적 공간 필요

3. 버스 장치에 대한 좋은 성능 확장

4. 상세한 오류 검출 및 보고 구조(Advanced Error Reporting, AER)

5. 핫스왑(Hot Swap) 기능

이러한 특징들로 PCIe(PCI Express)는 그래픽카드뿐만 아니라 FPGA 통신, SSD, NVMe, TV 수신 카드, 기가비트 이더넷(Gigabit Ethernet) 등에서 활용되고 있습니다.

※ 참고로 제가 조금 알고있는 내용과 검색한 내용을 정리한 정보입니다. 틀린 점이 있을 수 있으니 이점 참고하시기 바랍니다.

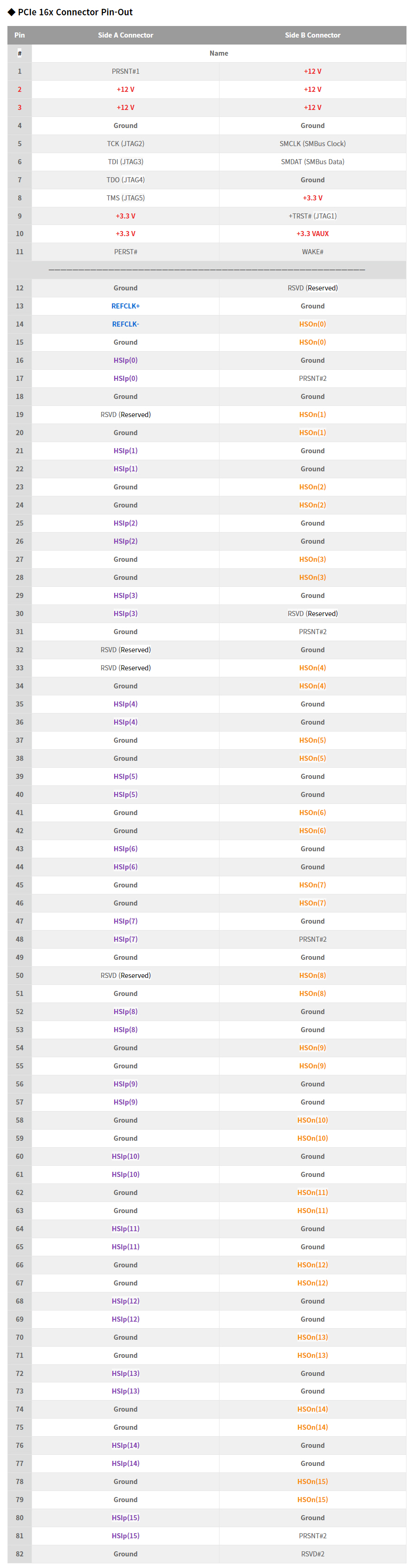

■ PCIe(PCI Express) Pin Map 분석 - PCI-Express 16x

다음으로 PCIe Pin Map을 분석해보겠습니다.

분석 기준은 그래픽카드에서 사용되는 PCIe 16x Connector Pin-Out입니다.

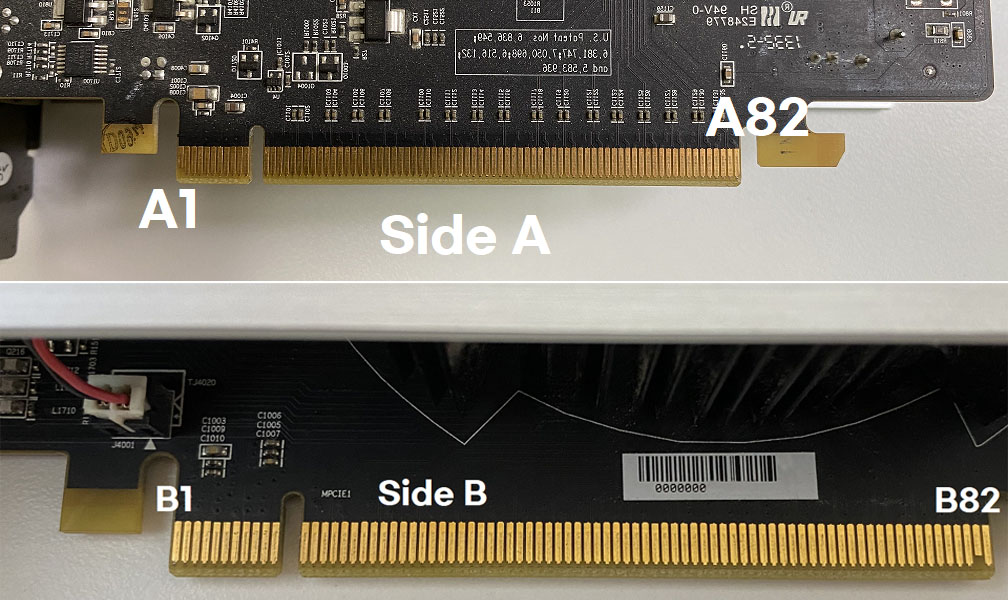

사진은 제가 보유하고 있는 구형 그래픽 카드입니다. 구형 그래픽카드이지만 PCIe Pin Map의 규격은 동일합니다. 그러므로 사진에서 Pin의 위치를 참고해주시기 바랍니다.

PCIe Pin Map을 기준으로 추가적인 보충 설명을 드리겠습니다.

Pin Map 앞쪽부터 보시면 전압 Pin들과 상대적으로 Low Speed 통신 Pin들이 확인됩니다.

전압은 +12[V]와 +3.3[V]를 사용합니다. JTAG 통신과 SMBUS 통신 Pin들도 있습니다.

다음으로 High Speed 통신 일명 고속 통신을 사용하는 Pin들이 확인됩니다. 통신에서 가장 중요한 Reference Clock Differential pair(REFCLK+, REFCLK-)가 있고 다음으로 순차적으로 HSIp(0) ~ HSIp(15), HSOp(0) ~ HSOp(15) Differential pair들이 있습니다.

Lane은 16 Lane이므로 Differential pair로 16개씩 있으며 HSIp는 Receiver Lane이고 HSOp는 Transmitter Lane입니다. 그리고 중간에 간혹 RSVD (Reserved) Pin들이 있습니다. 해당 Pin들은 사용하지 않는 Pin들은 아니며 그래픽 카드 제조사마다 추후 기능 확장(커스터마이징)을 위해 사용할 수 있도록 만든 Pin으로 알고 있습니다. 추가적으로 Hot plug present detect(PRSNT#2) Pin과 Hot Plug Detect(RSVD#2) Pin도 있습니다.

이상으로 PCIe 16x Connector Pin Map 분석을 마치겠습니다. 긴 글 읽어주셔서 감사합니다.

다음 포스팅은 보유하고 있는 구형 그래픽 카드를 가지고 Artwork 분석을 진행해보겠습니다.

<자료원문: https://designusefulthings.tistory.com/33 >

| |

관리자 * http://www.master4u.net